AMD рассказала об архитектуре Zen на конференции Hot Chips

В ходе мероприятия Hot Chips 28, традиционно проводимого в Стэнфордском университете, компания AMD обнародовала новую порцию сведений о готовящихся 14-нм процессорах с микроархитектурой Zen. Напомним, что чипмейкер планирует выпустить CPU Summit Ridge и APU Raven Ridge в следующем году, а пока ограничивается демонстрацией их инженерных семплов.

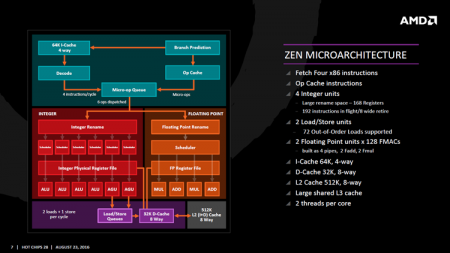

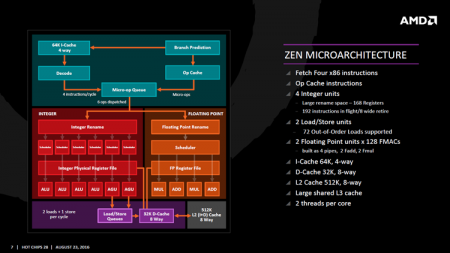

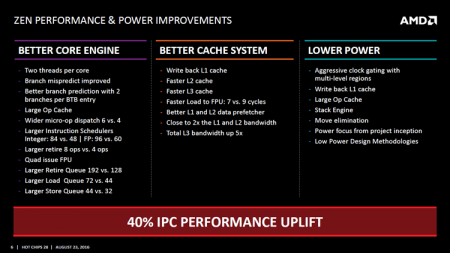

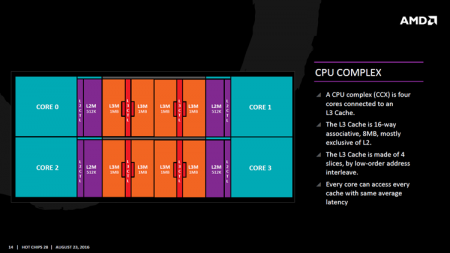

В состав одного ядра Zen включены четыре блока целочисленных операций (ALU) и два 128-битных FMAC (блок умножения — сложения). Объём 4-канального кеша инструкций равен 64 Кбайт, 8-канального кеша данных — 32 Кбайт. Кеш-память второго уровня с 8-канальным доступом имеет объём 512 Кбайт, а разделяемый кеш третьего уровня выполнен в виде блоков по 1 Мбайт.

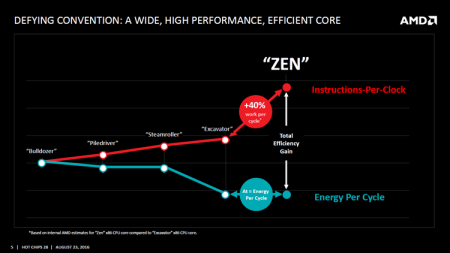

AMD постоянно напоминает, что процессоры Zen могут выполнять на 40 % больше инструкций («работы») за один такт по сравнению с чипами Excavator. На нижеприведённом графике также изображена нисходящая кривая «энергопотребление/такт».

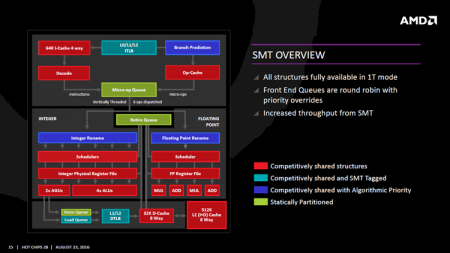

Zen поддерживает многопоточную обработку данных (Simultaneous Multi-Threading), содержит улучшенный предсказатель переходов, более «вместительные» блоки кеша операций и очередей. Кеш-память первого уровня имеет функцию обратной записи; пропускная способность различных уровней кеша выросла на величину от двух до пяти раз.

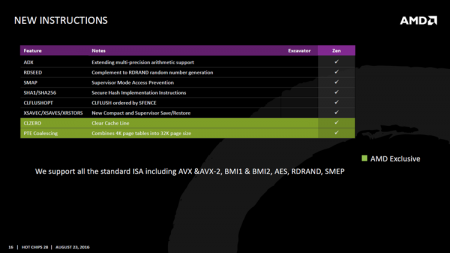

14-нм процессоры AMD получили восемь новых инструкций, включая эксклюзивные (не применяющиеся Intel) инструкции CLZERO и PTE Coalescing. Первая очищает содержимое кеш-памяти, а вторая объединяет 4-Кбайт таблицы страниц в 32-Кбайт страницы.

Одна из наиболее интересных особенностей Zen — «нарезанный» блоками по 2 Мбайт (2× 1 Мбайт) разделяемый кеш третьего уровня. Обращение любого из четырёх ядер модуля Zen к любому блоку кеша L3 занимает примерно одно и то же время. На один четырёхъядерный модуль (CPU Complex, CCX) приходится 8 Мбайт кеш-памяти третьего уровня. Вероятно, недорогие 4–8-ядерные процессоры Summit Ridge будут обладать неполным объёмом кеша L3 — 8 Мбайт и/или 12 Мбайт из максимально возможных 16 Мбайт.

Большинство операционных блоков ядер Zen эффективно используются как в однопоточном, так и в двухпоточном (SMT) режиме. Исключение составляют очереди микроопераций (micro-op), ухода (retire) и хранения (store).

В 2017 году мы станем свидетелями анонсов самых разных процессоров Zen — от встраиваемых до серверных, от 2- до 32-ядерных, от 4-ваттных до, как минимум, 95-ваттных.

Источник:

http://www.3dnews.ru/938236/?feed

- Связь Скорпиона и Весов: Роман-драма, страстная любовь, прогноз брака

- Гороскоп Овна на сентябрь: Новые идеи, важный переворот полнолунья, финансовый подъём

- Овен гороскоп 2021: Мощный толчок Юпитера, переезд, переворот судьбы

- «Любовь на рабочем месте»: Скорпионам астролог предсказал бурный роман в августе

- Натальная карта меняет судьбы: Как прочитать гороскоп рождения